ASML认为,摩尔定律还可持续10年甚至更久。 (示意图/达志影像/shutterstock)

摩尔定律是否走到极限一直是半导体业界热议的焦点,每一个制程世代质疑摩尔定律失效的声音也从未间断。独家供应半导体微影设备大厂艾司摩尔(ASML)近日在一篇文章中指出,现有技术能实现1奈米制程,摩尔定律可持续生效10年甚至更长时间。而台积电为巩固现有技术优势,正朝向1奈米等更先进制程迈进。

摩尔定律是美国半导体大厂英特尔(Intel)创办人之一戈登.摩尔(Gordon Moore)在1965 年所提出。电晶体数量左右了晶片的效能,摩尔当时发现,每个晶片上可容纳电晶体数目,会按照几何级数的法则增长,每1年约会增加1倍,运算性能提升 40%。

IT之家报导,ASML表示,在半导体领域,摩尔定律—这诞生于1965 年的前瞻推断,扮演着如同光一样的角色,指引晶片制造的每一次创新与突破,在过去的50 多年里,摩尔定律不断演进。

摩尔关于以最小成本制造复杂晶片的最初预测,也在演进过程中被转述成各种各样的表述,现在这个定律最常被表述为半导体晶片可容纳的晶体管数量呈倍数增长。 1975 年,摩尔修正自己预测:晶体管数量翻倍的时间从最初的1年上升到2年。

报导指出,摩尔认为,增加晶片面积、缩小元件尺寸以及优化器件电路设计是实现晶体管数量翻倍的三个重要因素。

ASML称,在过去的15 年里,很多创新方法使摩尔定律依然生效且状况良好。从整个行业的发展路线来看,它们将在未来10年甚至更长时间内,让摩尔定律继续保持这种态势。

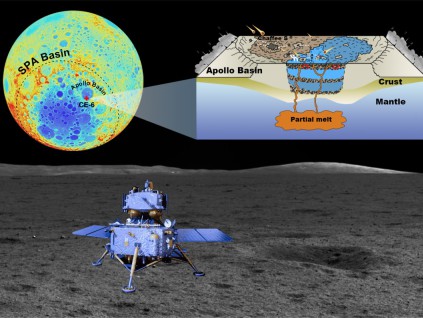

在元件方面,目前的技术创新足够将晶片的制程推进至少1奈米节点,此外,光刻系统分辨率的改进(预计每6 年左右缩小2 倍)和边缘放置误差(EPE)对精度的衡量也将进一步实现缩小晶片尺寸。

ASML强调,「只要我们还有想法,摩尔定律就会继续生效。」